的时候总会蹦出“FinFet工艺制造”之类的名词,那到底什么是FinFET工艺,到底有什么优势让国际大厂趋之若鹫?

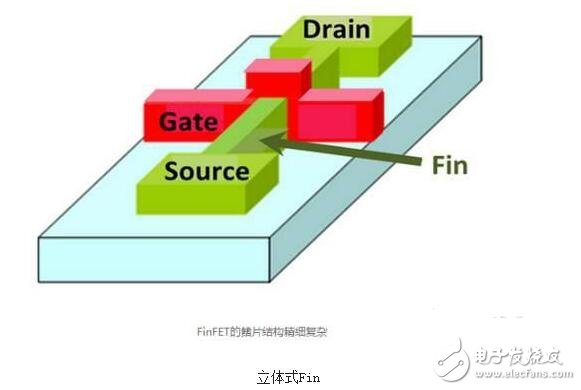

FinFET称为鳍式场效应晶体管(FinField-EffectTransistor),是由美籍华人科学家胡正明教授提出的,其中的Fin在构造上与鱼鳍非常相似,所以称为“鳍式”,而FET的全名是“场效电晶体”。

FinFET是一种新的互补式金属氧半导体(CMOS)晶体管,源自于传统标准的晶体管—“场效晶体管”的一项创新设计。

传统晶体管结构是平面的,所以只能在闸门的一侧控制电路的接通与断开。但是在FinFET架构中,闸门被设计成类似鱼鳍的叉状3D架构,可于电路的两侧控制电路的接通与断开。这种叉状3D架构不仅能改善电路控制和减少漏电流,同时让晶体管的闸长大幅度缩减。

最早使用FinFET工艺的是英特尔,他们在22纳米的第三代酷睿处理器上使用FinFET工艺,随后各大半导体厂商也开始转进到FinFET工艺之中,其中包括了台积电16nm、10nm、三星14nm、10nm以及格罗方德的14nm。

不过FinFET工艺的极限是7nm制程,第一代的7nm工艺还将会继续使用FinFET工艺,但是接下来就需要依赖极紫外光刻机了。

前面提到的FinFET可以理解为立体的晶体管,传统平面的晶体管所采用的是FD-SOI工艺。虽然这几年的FinFET工艺占据了大多数人的视线,但是FD-SOI工艺依然非常重要。

如果要是FinFET工艺核FD-SOI达到相同性能,FD-SOI工艺在制造过程中相对简单,但是SOI基片价格稍贵,而FinFET工艺虽然制造过程更为复杂,但是由于基片价格便宜,让两者的实际制造成本相差不大。

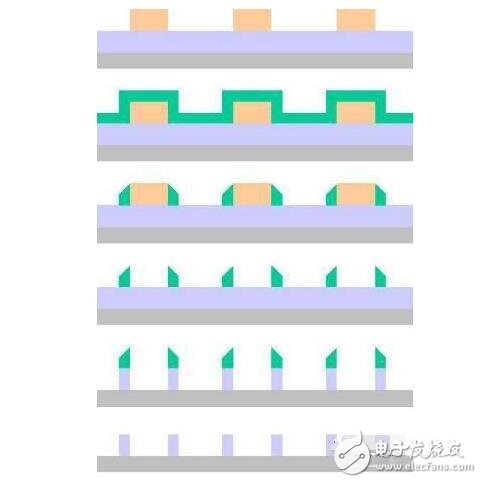

其中的Double Patterning是目前主流的FinFET制造工艺。它的原理就是先pattern一批80nm精度的图样,然后再交错Pattern一批80nm精度的图样;在两次光刻之后,就可以将精度提升到40nm。

特尔的做法就是先用普通精度的光刻可出一堆“架子”,然后在架子上沉淀一层很薄的硅,再选择性的使用把多余的材料弄走,剩下立着的就是超薄的Fin了。准确点来说,这个Fin不是刻出来的,而是长出来的。

FinFET工艺实质上就是再原油的基础上增加了一个栅极,这样可以让尺寸很小的晶体管减少漏电。因为大部分的漏电是来自于沟道下方的流通区域,也就是短沟道效应。

就有人开始想:既然电子是在沟道中运动,物理模型需要这片区域来平衡电荷,所以就有了沟道下方的耗尽层。但在短沟道器件里面,把耗尽层和沟道放在一起,等着漏电流白白地流过安博平台 安博体育在线去。

台积电去年宣布,计划联合ARM、Xilinx、Cadence,共同打造全球首个基于7nm工艺的芯片。

更确切地说,这四家半导体大厂将采用台积电7nm?FinFET工艺,制造一款CCIX(缓存一致性互联加速器)测试芯片,2018年第一季度完成流片。

该芯片一方面用来试验台积电的新工艺,另一方面则可以验证多核心ARM?CPU通过一致性互连通道与片外FPGA加速器协作的能力。

这款测试芯片基于ARMv8.2计算核心,拥有DynamIQ、CMN-600互连总线,可支持异构多核心CPU。

Cadence则提供CCIX、DDR4内存控制器、PCI-E?3.0/4.0总线、外围总线等IP,并负责验证和部署流程。

7nm将是台积电的一个重要节点(10nm仅针对手机),可满足从高性能到低功耗的各种应用领域,第一个版本CLN?7FF保证可将功耗降低60%、核心面积缩小70%,2019年则退出更高级的CLN?7FF+版本,融入EUV极紫外光刻,进一步提升晶体管集安博平台 安博体育在线成度、能效和良品率。

随着三星10纳米制程借高通骁龙835处理器的亮相,以及由台积电10纳米制程所生产的联发科HelioX30处理器,在魅族Pro7系列手机首发,之后还有海思麒麟970及苹果A11处理器的加持下,手机处理器的10纳米制程时代可说是正式展开。而对于下一代的7纳米制程,当前来看,应该仍是三星与台积电两大龙头的天下。由于在7纳米制程中,极其依赖的极紫外光(EUV)设备,中国厂商在短期间内仍无法购买到。这对于正积极建构自身半导体生产能量的中国来说,将可能在7纳米这个制程节点上被拉远距离。

事实上,对于7纳米制程,三星和台积电两大晶圆代工龙头都早已入手布局,以便争夺IC设计业者们的订单。其中,日前传出三星原定在2018年破土动工的韩国华城18号生产线,动工时间已经被提前到了2017年的11月,以便在2019年能够进入7纳米制程的量产阶段。其中,18号生产线多台极紫外光(EUV)设备,以强化生产效能。

至于,台积电在7纳米制程的布局,根据台积电高层之前在法说会上的说法,表示目前已经有12个产品设计定案,这使得第一代7纳米制程将会在2017年底或2018年达成量产。至于,第二代的7纳米制程则会在2019年达成量产的目标,制程中也将导入EUV的技术。因此,在不论是三星,或者台积电都将在7纳米制程上都将引入EUV技术的情况下,而这种被视为延续摩尔定律的设备,正是被寄望能推动未来制程进步的重要关键。

因此,就7纳米制程这个节点的状况来看,在一定程度上也是被EUV设备所控制,而EUV设备却是被荷兰半导体设备厂商艾司摩尔(ASML)所控制的。ASML是一家从事半导体设备设计、制造及销售的企业,自1984年从飞利浦独立出来之后,在2016年先后宣布收购汉微科及蔡司半导体24.9%股份。而这家垄断了高端光刻机市场的厂商,其股东中就包含英特尔(intel)、台积电和三星。根据ASML公布的2017第2季财报,公司单季的营收净额为21亿欧元,毛利率为45%。

由于,EUV的研发难度非常大。因此,也造成单价的居高不下,每一台的价格约在高昂1亿欧元上下。而且,这种价值连城的设备还不是有钱就能买到的。例如受限于《瓦圣纳协定(TheWassenaarArrangementonExportControlsforConventionalArmsandDual-UseGoodandTechnologies)》,中国的厂商就买不到这种最高阶的光刻机设备。此外,由于ASML的EUV年产量也只有12台,包括三星及台积电几乎已经抢光了2017到2018年所有产能的情况下,即便有报导称ASML正在提升生产效率,希望在2018年将产能增加到24台,2019年达到40台,但仍不足以应付市场的需求。使得中国厂商即使有机会购买EUV设备,短期恐怕也都要落空。

当前,对于大力投入集成电路发展的中国来说,虽然买不到ASML的EUV设备,但是也寻找其他方式希望能有所突破。例如2017年3月,上海微电子装备(集团)就与ASML签署了合作备忘录。6月时,上海集成电路研究开发中心又宣布与ASML合作,将共同建立一个培训中心。另外,由中国本地的长春光机所带领的极紫外光刻关键技术研究专案,也在2017年6月启动。而这些计划,都是中国希望能在EUV设备销售限制上能有所突破准备。但是,实际上在未来是不是真的能有所进展,达成最后的目标,就还有待日后的持续观察。

近日,根据外媒MacRumors报道,苹果公司已经选择台积电作为A12处理器的独家代工商,预计2018年下半年推出的三款新iPhone将采用该处理器。报道援引苹果公司供应链中匿名消息人士的线nm工艺制造,在封装体积更小的同时性能更加强大。

消息透露,台积电7nmFinFET制程工艺相比三星更加具有竞争力。韩国先驱报去年7月报道,三星已经签订了一项协议,为苹果供应部分A12芯片,但两天后,Digitimes报道,台积电仍然可能独享所有的A12芯片订单。

目前台积电已经是iPhone8、iPhone8Plus和iPhoneX所搭载的的A11仿生芯片的独家代工商。如果报道属实的话,那么三星将再次错失苹果的巨额订单。唯一值得安慰的是高通的高端芯片仍然由三星独家代工,但随着三星高端芯片的成熟,高通很可能会寻找新的代工商。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。举报投诉

,其所生产的芯片已经超过10亿颗。此外,台积电官网还披露了一个消息,其6

All Programmable 技术和器件的全球领先企业赛灵思公司(Xilinx, Inc. (NASDAQ:XLNX))今天宣布其与台积公司( TSMC)已经就

和3D IC技术开展合作,共同打造其下一代All Programmable FPGA、MPSoC和3D IC。

GlobalFoundries已经决定不走寻常路了,他们确认会取消10

生产有可能将会从 2018 年的第一季度提前至 2017 年的第四季度。这就

,如果苹果下一代 iPhone 的处理器真的完全由台积电来供应,那么后者的

处理器也会在明年下半年发布,而GlobalFoundries已经确定跳过10

LPP采用EUV光刻,机器采购自荷兰ASML(阿斯麦),型号为双工件台NXE:3400B(光源功率280W),日产能1500片。

智能座舱芯片行业竞争分析:原材料、市场应用、产品种类、市场需求、市场供给,下游

基本完工开始试产:面积缩小45%、性能提升15%.pdf(105.52 KB)

技(Synopsys, Inc., 纳斯达克股票市场代码: SNPS)近日宣布,在设计人员的推动下,Fusion Design Platform™已实现重大

就是硅材料芯片的物理极限,碳纳米管复合材料又是怎么一回事呢?面对美国的技术突破,中国应该怎么做呢?XX

450 万个门、包含数十亿个晶体管的时钟电路上;跟踪需要 4.5 小时,仿线 个 CPU 上运行。总结设计

节点的 SoC 是一项艰巨的任务,需要专业的时钟分析知识以确保首次通过硅片成功。原作者:EETOP编译整理

的宽度,也被称为栅长。栅长越短,则可以在相同尺寸的硅片上集成更多的晶体管。目前,业内最重要的代工企业

,共同致力于有机、透明与软性的电子研究。“有机半导体将成为信息时代的‘原油’,届时,摩尔定律也将在

节点达到极限,”TU Dresden有机组件研究主席Stefan Mansfield表示

(对应都是MOS管栅长),目前也有了很多实验室在进行一些更小尺寸的研究。随着MOS管的尺寸不断的变小,沟道的不断变小,出现各种

公司第二代使用极紫外光(EUV)技术的制程,其已展现优异的光学能力与符合预期的良好

目前的GS464V升级到LA664,因此单核性能有较大提升,达到市场上主流设计。至于未来的

ARM芯片,不过代工厂商GlobalFoundries却爆料,“AMD下代处理器将直奔

竞争的帷幕。 Intel宣布投资70亿美元升级Fab 42工厂,3-4年后准备生产

生产下一代高端芯片骁龙 845 / 840,对于这个笔者认为很可能是又一个谎言!

此前,AMD公布的路线图显示,明年AMD会拿出Zen 2处理器,它会采用

上,三星已经深知落后台积电不少,后者除了手握苹果、联发科、华为客户外,还凭借

本周在火奴鲁鲁举行的VLSI(超大规模集成电路)研讨会上,三星首次分享了基于EUV技术的

芯片,苹果这一出手让高通和三星汗颜,而苹果此次合作的代工厂是台积电,由此可见,台积电在制造

有望在性能、功耗、芯片面积上都有显著的改善,而且很可能会被用于制造业界最强大的移动处理器。

量产下月出货,毫无疑问,在苹果A12将首次搭载,下半年台积电的运营也将进入旺季。

,并且会交由台积电独家生产;高通骁龙855、华为麒麟980等处理器也将采用

技术处理器晶片虽然面积没有减少,但是进步表现在主频的提升上。官方表示,至于

如果没有意外,苹果今年的旗舰手机将会配备台积电生产的A12芯片,该芯片采用

,在目前位置已经算非常先进了。不过最新消息称,苹果下代A13芯片,还是会采用

在日前举行的Computex 2018发布会上,AMD有些出人意料地进行了高规格的产品发布,公开的产品包括下一代使用

上没什么对比性,当然实际性能就不一定了,因此我们可以主要来谈谈AMD的

,而打头阵的无疑是移动芯片,目前已知的包括苹果Apple A12/华为麒麟980以及高通骁龙855都是基于

麒麟970一样,华为手机处理器再度在去全球领先。和麒麟970相比,麒麟980会有哪些提安博官网 安博体育升?虽然华为没有公布数据,但我们可以从目前台积电公布的

的可怕竞争,最近又难倒了一位参赛选手。格罗方德(GlobalFoundries)今日宣布,它将无限期地暂停

,英特尔、三星、台积电、格罗方德等知名的半导体代工企业均有这样的实力。

AMD Zen架构取得了空前成功,今年还优化为Zen+增强版,并有同样优化的12

5月29日,在今天的台北国际电脑展上,联发科对外发布全新5G移动平台,该款多模 5G系统单芯片(SoC)采用

在日本的2019 VLSI Symposium超大规模集成电路研讨会上,台积电宣布了两种新

日前,高通发布了新一代旗舰平台骁龙865、主流平台骁龙765/765G,分别采用台积电

产能现在要抢,AMD的锐龙3000高端型号也遭遇了供不应求的问题,那AMD会使用三星代工吗?

显卡之外,AMD的桌面锐龙、HEDT发烧处理器、服务器霄龙及笔记本锐龙APU四大产品线

显卡之外,AMD的桌面锐龙、HEDT发烧处理器、服务器霄龙及笔记本锐龙APU四大产品线

一直是国内的痛点,所以国内最大的晶圆代工厂中芯国际任重而道远。此前中芯国际已经表态14

已经试产,今年就会迎来一轮爆发,年底的产能将达到目前的3-5倍,同时今年内还有可能试产更先进的

制程方面,台积电的进度明显要快于英特尔。其实在2017年的时候,英特尔就指出台积电

。而且英特尔呼吁行业应该统一命名标准,防止命名混乱。英特尔更希望以晶体管密度作为衡量标准。

可以进一步提升芯片的晶体管密度,提升性能并降低功耗,可广泛用于PC、智能手机等设备的元器件中。

是数字游戏,Intel被大家误会了。不过今年Intel推出了新一代的10

这几天发布Q3季度财报之后,Intel的股价跳水了10%,损失了1700多亿的市值,一方面是Q3利润下滑,一方面还是跟Intel

,AMD、苹果、高通、NVIDIA等公司也会跟着受益,现在自己生产芯片的就剩下Intel了,然而安博官网 安博体育它们的

的锐龙5000、RDNA2架构的RX 6000系列显卡,不过上市一两个月来还是在缺货,原因是

的产能,也就有了给予其他厂商更多的可能,去年下半年 AMD 获得的产能

芯片已经被IBM研制出来了,在这一颗指甲盖大小面积的芯片上可以容纳500亿颗晶体管,芯片制程

密度高3.3倍,性能提升达到了35%以上,同样性能下功耗减少了65%,在当时

更小的芯片,5纳米芯片要优于7纳米芯片,但是最终还是要看机器是否能够发挥芯片的最大功效。

在芯片设计和制造中,纳米表示的是芯片中晶体管与晶体管之间的距离,在体积相同大小的情况下,

0512-52218767